北京大學黃如院士團隊在“存內計算AI芯片”領域取得重要成果

2022年2月末,有著“集成電路國際奧林匹克盛會”之稱的IEEE國際固態(tài)電路會議(International Solid-State Circuits Conference, ISSCC)圓滿舉辦。ISSCC是世界學術界和企業(yè)界公認的集成電路設計領域最高級別會議。

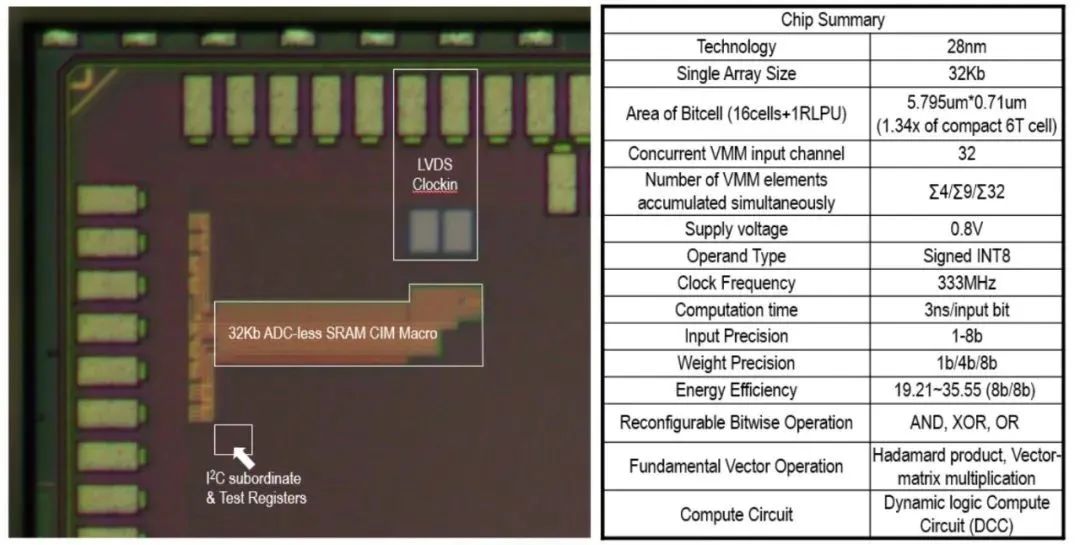

在此次會議上,北京大學集成電路學院與人工智能研究院黃如院士——燕博南助理教授課題組關于存內計算的的學術文章《A 1.041Mb/mm2 27.38TOPS/W Signed-INT8 Dynamic Logic Based ADC-Less SRAM Compute-In-Memory Macro in 28nm with Reconfigurable Bitwise Operation for AI and Embedded Applications》收錄于“Session 11 存內計算與SRAM”專題(文章號11.7)。

此工作提出高效的無ADC架構SRAM存內計算加速引擎,基于28nm工藝搭建模塊可以達到27.38TOPS/W@INT8的高能效比,同時實現(xiàn)高達1.041Mb/mm2密度,達到國際領先指標并實現(xiàn)技術突破。

該工作合作者有北京蘋芯科技有限公司、NeoNexus Group與杜克大學。課題組獲得了北京大學人工智能研究院、北京蘋芯科技等資助。

下附本工作與課題組的簡介:

全數(shù)字型存內計算技術路線

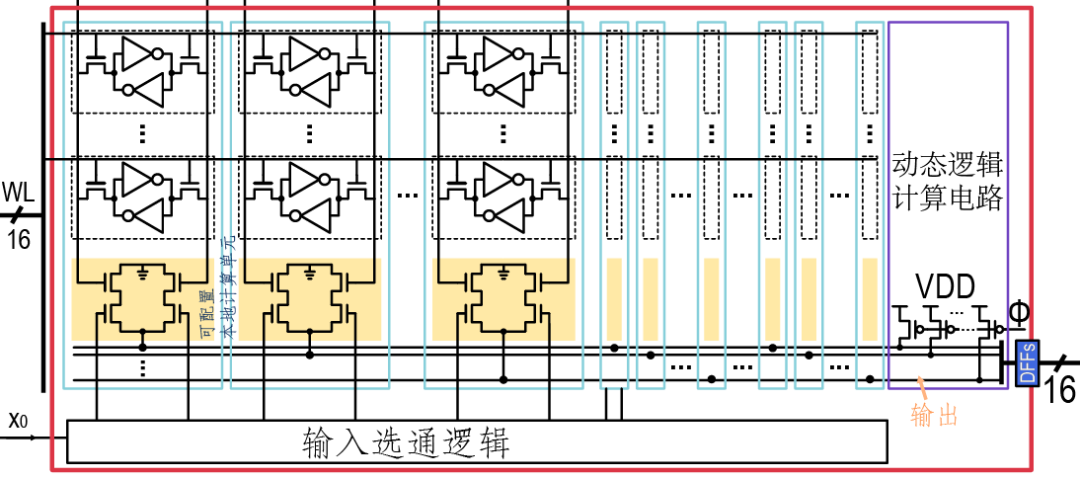

此工作實現(xiàn)了28nm 技術節(jié)點的32Kb無 ADC的SRAM存內計算加速單元,由動態(tài)邏輯計算電路替代傳統(tǒng)模數(shù)轉換或CMOS靜態(tài)邏輯,達到高能效比與面效比。同時由分布于存儲器陣列內的可重構本地處理單元(Reconfigurable Local Process Units,RLPU)實現(xiàn)bitcell級的數(shù)組邏輯運算,并拓展至向量矩陣相關計算(VHP/VMM),在核心指標方面相較于傳統(tǒng)架構具備數(shù)量級優(yōu)勢,為存內計算技術的實際產業(yè)化應用部署奠定堅實基礎。

存內計算芯片演示

存內計算芯片主要用于深度學習網絡中海量乘加計算的加速。課題組還利用原型芯片進行了常見的神經網絡的實際演示,在ISSCC的演示環(huán)節(jié)受到廣泛好評。演示視頻鏈接:

https://www.bilibili.com/video/BV15b4y1H7gP

黃如院士-燕博南助理教授課題組簡介

燕博南助理教授, 2020年于美國杜克大學獲得電子與計算機博士學位,后入職北京大學人工智能研究院從事人工智能與芯片交叉方向研究。主要研究方向包括:

· 新興存儲器集成電路設計

· 存算一體化電路與系統(tǒng)

· 人工智能計算機微架構

課題組常年招收志在探索未知、勇于創(chuàng)新的本科生與研究生,合作與招生相關問題請直接聯(lián)系Email:bonanyan@pku.edu.cn。

ISSCC會議介紹

ISSCC(IEEE International Solid-State Circuits Conference,國際固態(tài)電路會議),是世界學術界和企業(yè)界公認的集成電路設計領域最高級別會議,被認為是集成電路設計領域的“奧林匹克大會”。世界上第一個TTL電路、世界上第一個8位微處理器、世界上第一個1Gb的DRAM、世界上第一個GHz微處理器、世界上第一個多核處理器等眾多集成電路歷史上里程碑式的發(fā)明都在該會議上首次披露。自1954年以來,該會議已經成功舉辦68屆。本次存內計算論文入選意味著此項核心技術已達到國際領先水平,得到了學術界的頂會認可,代表了芯片領域新的前進方向,在AI技術應用程度不斷提升的今天,存內計算擁有巨大的發(fā)展前景。

您填的信息已提交,老師會在24小時之內與您聯(lián)系

如果還有其他疑問請撥打以下電話

中國人民大學

中國人民大學 中國政法大學

中國政法大學 清華大學

清華大學 對外經濟貿易大學

對外經濟貿易大學 首都經濟貿易大學

首都經濟貿易大學